- 您现在的位置:买卖IC网 > Sheet目录2007 > MAX1093AEEG+ (Maxim Integrated Products)IC ADC 10BIT 250KSPS 24-QSOP

MAX1091/MAX1093

250ksps, +3V, 8-/4-Channel, 10-Bit ADCs

with +2.5V Reference and Parallel Interface

_______________________________________________________________________________________

5

Note 1: Tested at VDD = +3V, COM = GND, unipolar single-ended input mode.

Note 2: Relative accuracy is the deviation of the analog value at any code from its theoretical value after offset and gain errors have

been removed.

Note 3: Offset nulled.

Note 4: On channel is grounded; sine wave applied to off channels.

Note 5: Conversion time is defined as the number of clock cycles times the clock period; clock has 50% duty cycle.

Note 6: Input voltage range referenced to negative input. The absolute range for the analog inputs is from GND to VDD.

Note 7: External load should not change during conversion for specified accuracy.

Note 8: When bit 5 is set low for internal acquisition, WR must not return low until after the first falling clock edge of the conversion.

TIMING CHARACTERISTICS (continued)

(VDD = VLOGIC = +2.7V to +3.6V, COM = GND, REFADJ = VDD, VREF = +2.5V, 4.7F capacitor at REF pin, fCLK = 4.8MHz (50% duty

cycle), TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25°C.)

tTR

20

70

ns

CLOAD = 20pF (Figure 1)

RD Rise to Output Disable

RD Fall to Output Data Valid

tDO

20

70

ns

RD Fall to INT High Delay

tINT1

100

ns

CS Fall to Output Data Valid

tDO2

110

ns

CLOAD = 20pF (Figure 1)

PARAMETER

SYMBOL

MIN

TYP

MAX

UNITS

CONDITIONS

HBEN to Output Data Valid

tDO1

20

110

ns

CLOAD = 20pF (Figure 1)

3k

3k

DOUT

VLOGIC

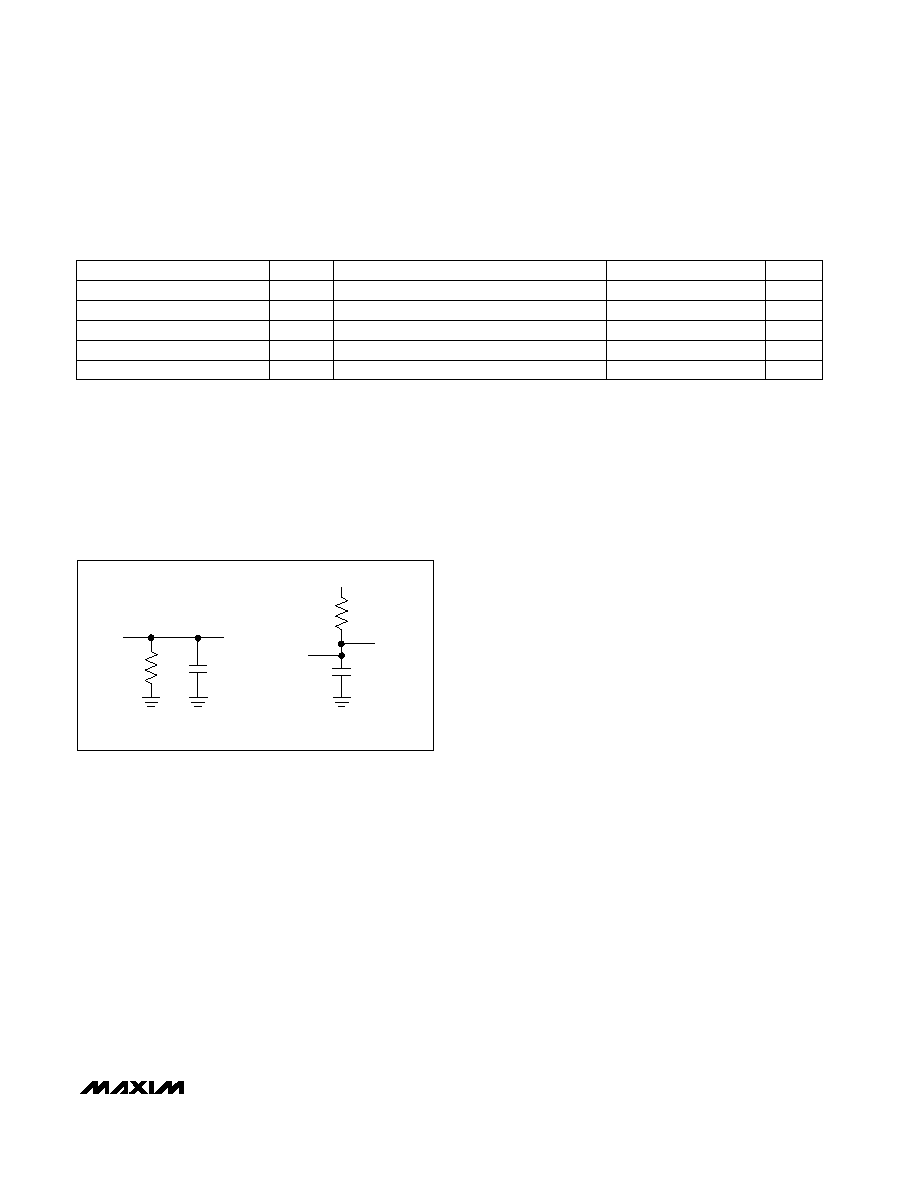

a) HIGH-Z TO VOH AND VOL TO VOH

b) HIGH-Z TO VOL AND VOH TO VOL

CLOAD

20pF

CLOAD

20pF

Figure 1. Load Circuits for Enable/Disable Times

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MAX1098CEAE+

IC ADC 10BIT SERIAL 16-SSOP

MAX11040GUU+T

IC ADC 24BIT 4CH 38-TSSOP

MAX11046ECB+T

IC ADC 16BIT PAR 250KSPS 64TQFP

MAX11046ETN+T

ADC 16BIT SAMPLING 8CH 56-TQFN

MAX11049ECB+

IC ADC 16BIT PAR 250KSPS 64TQFP

MAX1104EUA+

IC CODEC 8BIT 8-UMAX

MAX11100EUB+

IC ADC 16BIT SRL 200KSPS 10UMAX

MAX11101EUB+

IC ADC 14BIT SRL 200KSPS 10UMAX

相关代理商/技术参数

MAX1093AEEG+T

功能描述:模数转换器 - ADC 250ksps 4Ch 10-Bit w/Internal 2.5V ref RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1093AEEG-T

功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1093AEEI

功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1093BCEG

功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1093BCEG+

功能描述:模数转换器 - ADC 250ksps 4Ch 10-Bit w/Internal 2.5V ref RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1093BCEG+T

功能描述:模数转换器 - ADC 250ksps 4Ch 10-Bit w/Internal 2.5V ref RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1093BCEG-T

功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1093BEEG

功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32